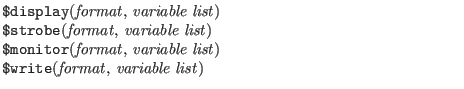

These commands have the same syntax, and display text on the screen during simulation. $display and $strobe display once every time they are executed, whereas $monitor displays every time one of its parameters changes. The difference between $display and $strobe is that $strobe displays the parameters at the very end of the current simulation time unit rather than exactly when it is executed. The format string is like that in C/C++, and may contain format characters. Format characters include %d (decimal), %h (hexadecimal), %b (binary), %c (character), %s (string) and %t (time), %m (hierarchy level). Forms like %5d, %5b etc. would assign a field width of 5 when printing the item.

$display and $write are the same except $display appends a newline if the string does not have a trailing newline character, $write does not do this.

Print a message starting with ``Fatal:'' or ``Warning:''.

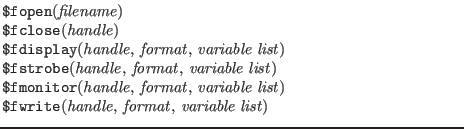

These commands write more selectively to files.

$fopen opens an output file and gives the open file an integer handle for use by the other commands.

$fclose closes the file and lets other programs access it.

In WRspice, there are two special handles that are automatically open and can't be closed.

0 Print to the pop-up error window. 1 or < 0 Print to the standard output (terminal window).

$fdisplay and $fwrite write formatted data to a file whenever they are executed. They are the same except $fdisplay appends a newline if the string does not have a trailing newline character, $fwrite does not do this.

$fstrobe also writes to a file when executed, but it waits until all other operations in the time step are complete before writing. Thus

initial #1 a=1; b=0; $fstrobe(hand1, a,b); b=1;will write write 1 1 for a and b.

$monitor writes to a file whenever any of its arguments changes.